MOSFET Basics

School of Electronics & Computing Systems

UNIVERSITY OF

Cincinnati

6.4, 6.5 – Real MOSFET, Inverters, Capacitance

2 Review

School of Electronics & Computing Systems

Cincinnati

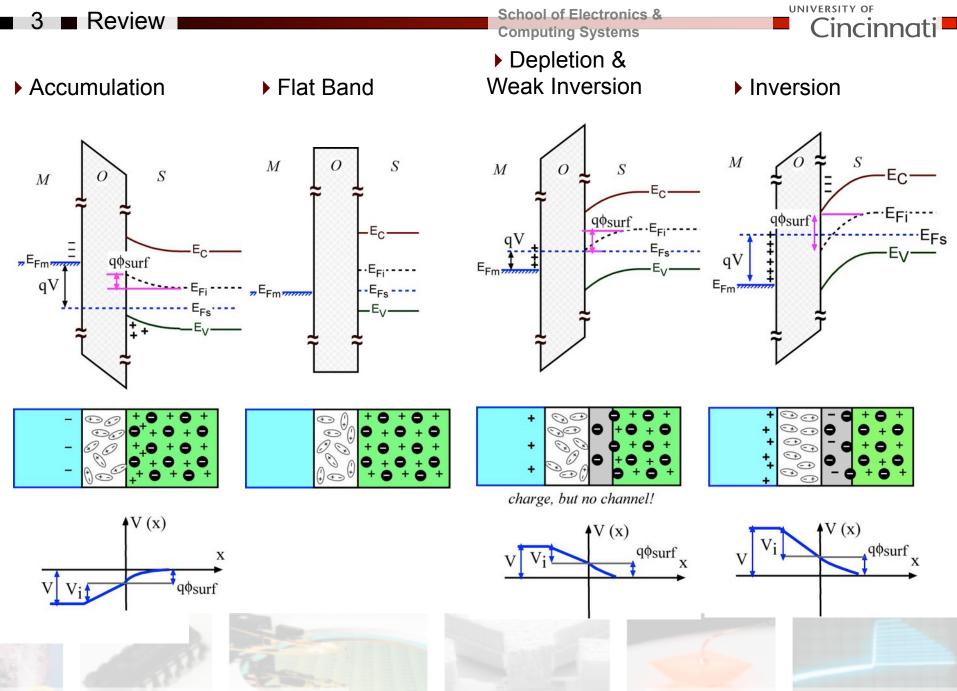

Bringing it all together (review)

- The depletion I can create under the gate oxide maximizes, why?

- Once above threshold voltage, at what mathematical rate are carriers created in the channel?

SECS 2077 – Semiconductor Devices ©

SECS 2077 – Semiconductor Devices ©

4 ■ Review Ideal MOSFET V<sub>TH</sub>

IDEAL CASE:

$$V_T = -\frac{Q_{d,max}}{C_i} + 2\phi_f$$

1) deplete holes  $Q_{d,\max} = -2\sqrt{\varepsilon_s q N_a \phi_F}$

2) get inversion (electrons and n-channel)  $\phi_F = \frac{kT}{q} \ln \frac{N_a}{n_i}$

SECS 2077 – Semiconductor Devices ©

School of Electronics & Computing Systems

School of Electronics & Computing Systems

Cincinnati

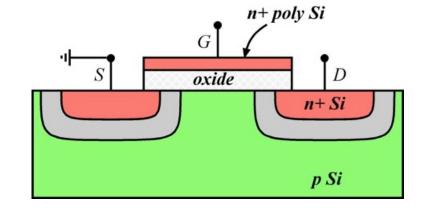

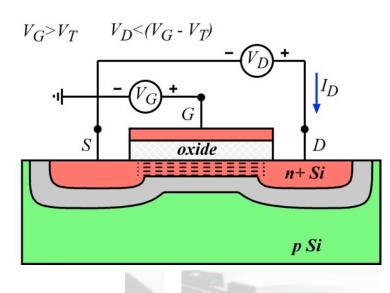

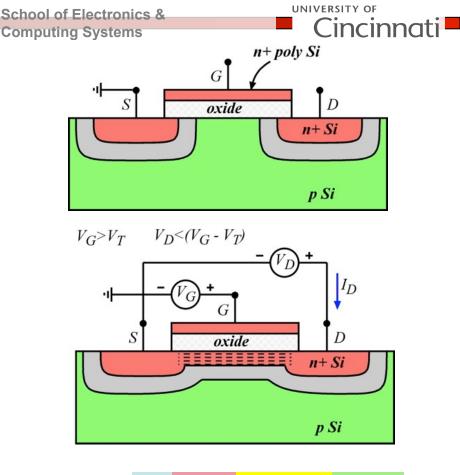

**REAL NMOS** (n-channel)

**IDEAL NMOS**

(*n*-channel)

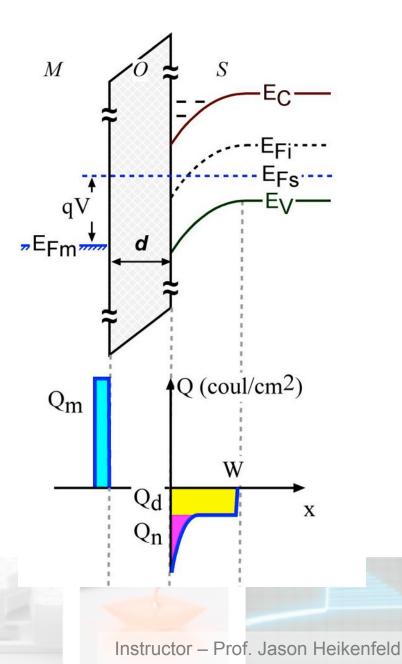

This is for V=0 (thermal equilibrium!, look at the Fermi levels...)

Why do the bands and oxide bend?

- Fermi levels line up, metal like n++ so all bend on Si side

- If bands bend, we have depletion net charge due to  $N_a^-$ , requires + charge on metal side... therefore a voltage!

School of Electronics & **Computing Systems**

UNIVERSITY OF lincinno

SECS 2077 – Semiconductor Devices ©

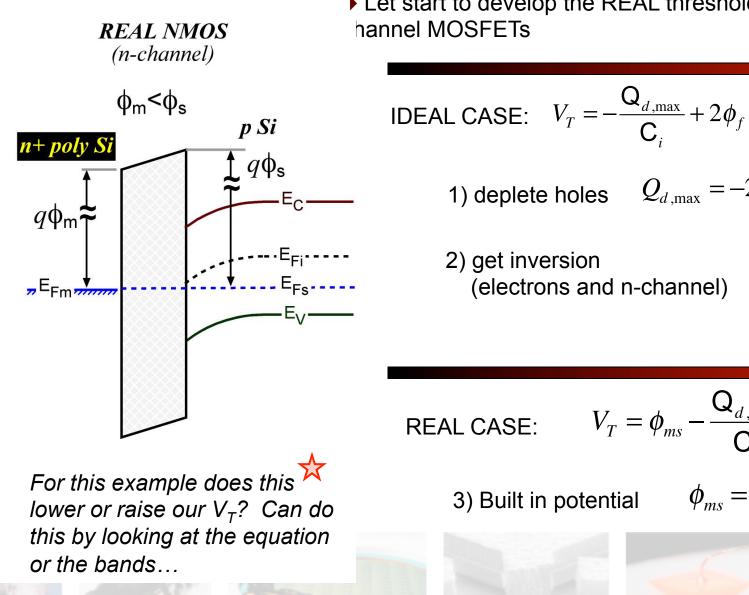

Let start to develop the REAL threshold voltage for n-

$Q_{d,\max} = -2\sqrt{\varepsilon_s q N_a \phi_F}$

(electrons and n-channel)

$$\phi_F = \frac{kT}{q} \ln \frac{N_a}{n_i}$$

$V_T = \phi_{ms} - \frac{\mathbf{Q}_{d,\max}}{\mathbf{C}} + 2\phi_f$

$$\phi_{ms} = \phi_m - \phi_s$$

UNIVERSITY OF School of Electronics & **Computing Systems**

Cincinna

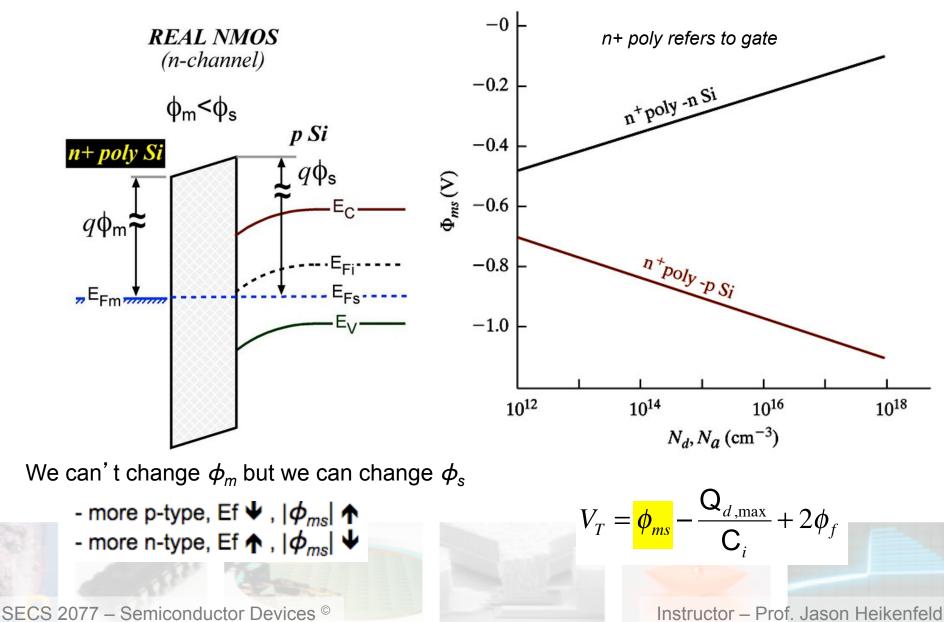

• Look at  $\phi_{ms} = \phi_m - \phi_s$  in more detail...

School of Electronics & Computing Systems

UNIVERSITY OF

Cincinnati

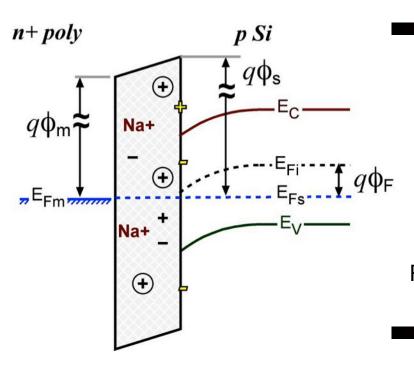

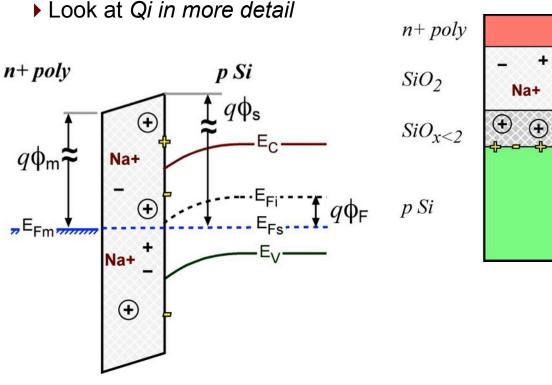

• We are not done yet! There are more non-ideal effects...

1) deplete holes  $Q_{d,\max} = -2\sqrt{\varepsilon_s q N_a \phi_F}$ 2) get inversion (electrons and n-channel)  $\phi_F = \frac{kT}{q} \ln \frac{N_a}{n_i}$ 3) Built in potential  $\phi_{ms} = \phi_m - \phi_s$ REAL CASE:  $V_T = \phi_{ms} - \frac{Q_{d,\max}}{C_i} + 2\phi_f$

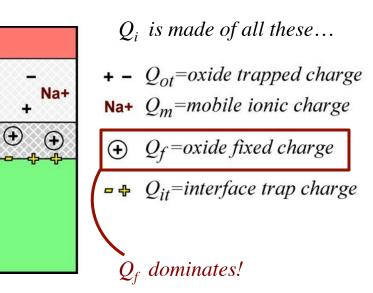

Couple types of charge: ionic, oxide, oxide/Si interface.

Oxide/Si interface charge often dominates and is often + (which attracts e-, means bands must bend down).

How will we add it to our  $V_T$  equation?

SECS 2077 – Semiconductor Devices ©

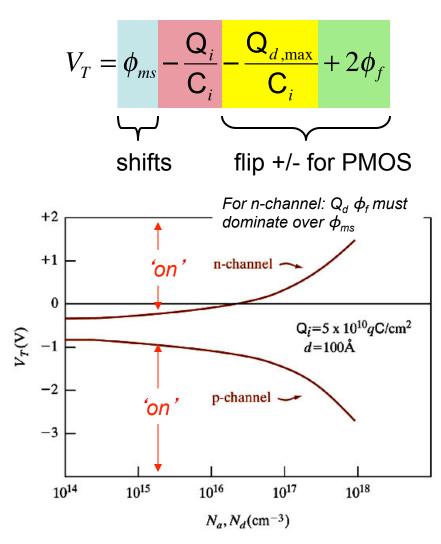

4) Interface Charge  $Q_i$

REAL CASE:

$$V_T = \phi_{ms} - \frac{Q_i}{C_i} - \frac{Q_{d,max}}{C_i} + 2\phi_f$$

School of Electronics & Computing Systems

Due to  $Q_f$ , the net  $Q_i$  is positive charge, pulls band down (lower  $V_T$ ).

Don't get confused,  $Q_d$ increases  $V_T$  since it is a negative charge!

$$V_T = \phi_{ms} - \frac{\mathbf{Q}_i}{\mathbf{C}_i} - \frac{\mathbf{Q}_{d,\max}}{\mathbf{C}_i} + 2\phi_f$$

SECS 2077 – Semiconductor Devices ©

Now we have the full story! Lets review...

IDEAL CASE:

$$V_T = \frac{-\frac{Q_{d,\text{max}}}{C_i} + 2\phi_f$$

**School of Electronics &**

**Computing Systems**

1) deplete holes

$$Q_{d,\max} = -2\sqrt{\varepsilon_s q N_a \phi_F}$$

2) get strong inversion

(electrons and n-channel)  $\phi_F = \frac{kT}{q} \ln \frac{N_a}{n_i}$

3) workfunctions

$$\phi_{ms} = \phi_m - \phi_s$$

4) interface charge  $Q_i$

REAL CASE:

$$V_T = \phi_{ms} - \frac{Q_i}{C_i} - \frac{Q_{d,max}}{C_i} + 2\phi_f$$

SECS 2077 – Semiconductor Devices ©

Instructor – Prof. Jason Heikenfeld

UNIVERSITY OF

Cincinnati

11 ■ Review! Take a break!

$\blacktriangleright$  What factors are needed for the ideal V<sub>T</sub> and do they increase or decrease V<sub>T</sub>?

$\blacktriangleright$  What factors are needed for the <u>real</u> V<sub>T</sub> and do they increase or decrease V<sub>T</sub>?

• What factors for the <u>real</u>  $V_T$  will change with doping level in the p Si substrate? *Hint, there are 3 of them...*

•  $\Phi_{ms}$ , for a n+ polycrystaline Si gate and a n+ substrate underneath the gate it should be approximately what? *This should be easy!*

$$V_T = \phi_{ms} - \frac{\mathsf{Q}_i}{\mathsf{C}_i} - \frac{\mathsf{Q}_{d,\max}}{\mathsf{C}_i} + 2\phi_f$$

$$g_m(sat.) = \frac{\partial I_D(sat.)}{\partial V_G}$$

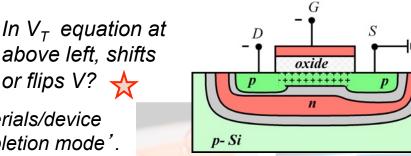

Note  $\Phi_{ms}$  and  $Q_i$  cause N-MOS to be 'on' at 0V...

... therefore in real MOS they must make some materials/device modifications or DC offsets. Otherwise it would be 'depletion mode'.

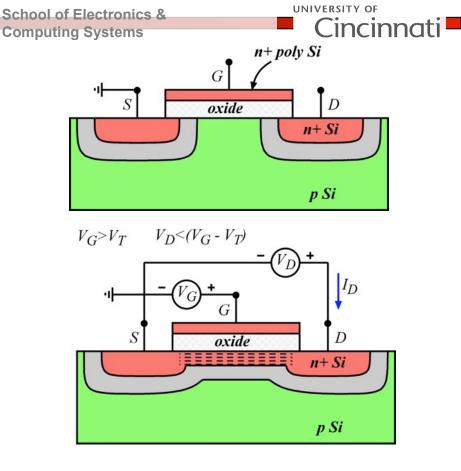

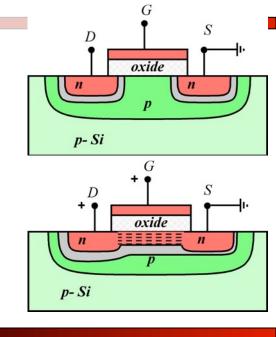

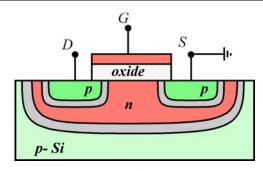

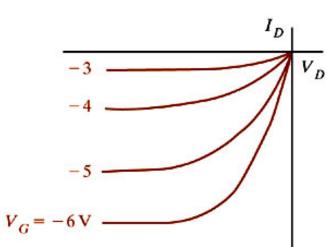

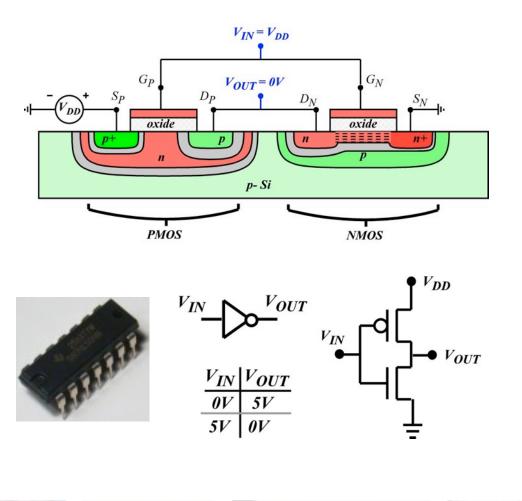

PMOS -p-channel -enhancement

School of Electronics &

**Computing Systems**

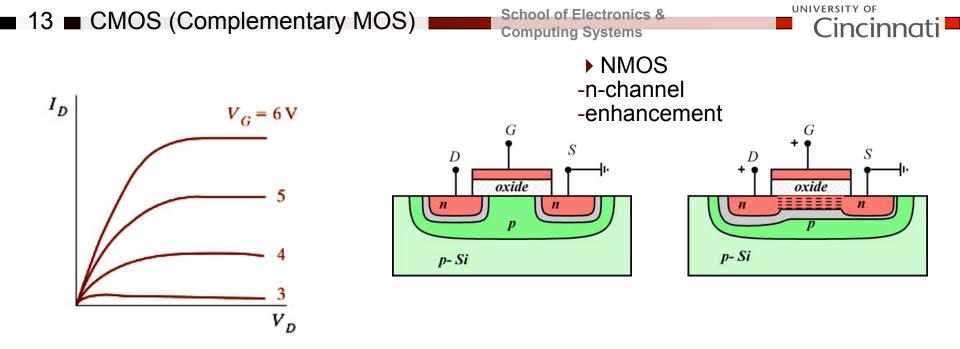

NMOS

-n-channel

-enhancement

Why p-Si substrate?

or flips V? 🛧

Instructor – Prof. Jason Heikenfeld

SECS 2077 – Semiconductor Devices ©

SECS 2077 – Semiconductor Devices ©

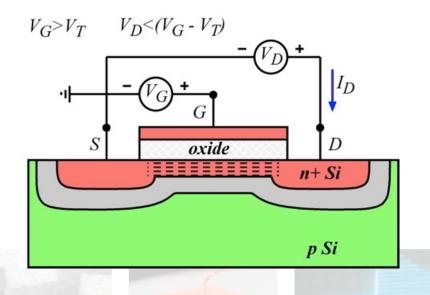

Note, they made  $V_D$  negative (you will see in two slides why they do this for an inverter...)

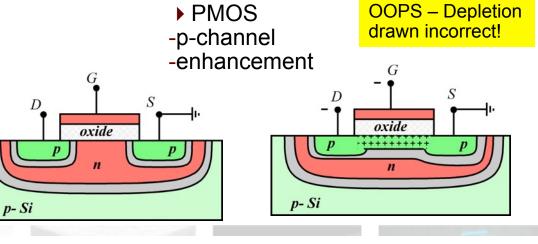

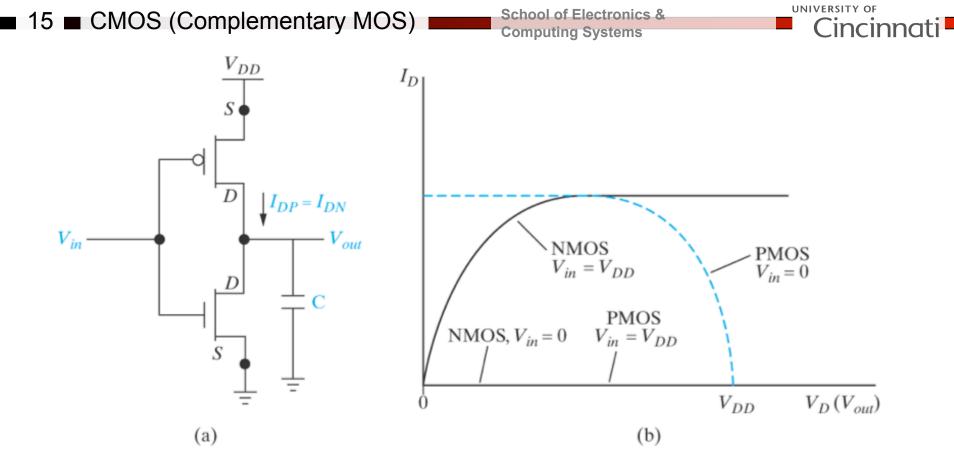

▶ This is a plot of the total current at Id for the PMOS (blue dotted line) and the NMOS (black line) vs. Vd....

It basically shows you that you want to lock Vd into a 0 or a 1, not in between, because then current flows through both transistors!

SECS 2077 – Semiconductor Devices ©

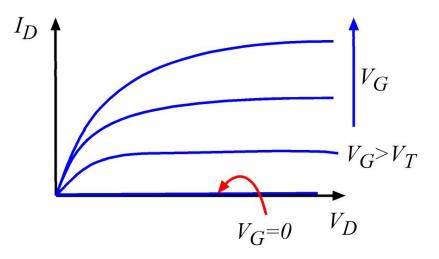

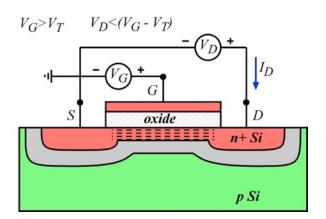

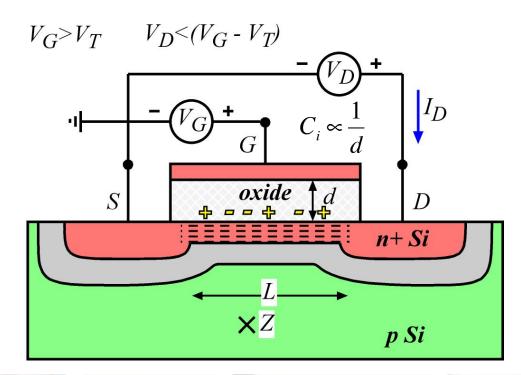

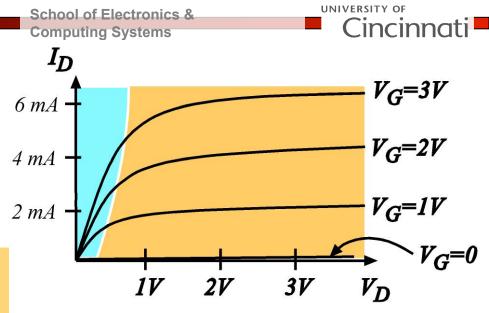

17 Drain Current

▶ It can be shown (6.5.1) that the NMOS drain current at low V<sub>D</sub> (not satur.) is:

$$I_d = \frac{\overline{\mu}_n Z \mathbf{C}_i}{L} \left[ (V_G - V_T) V_D - \frac{1}{2} V_D^2 \right]$$

SECS 2077 – Semiconductor Devices ©

► Larger current is often good for fast switching (RC)... look at equation at left and examine these factors:

UNIVERSITY OF

incin

- shorter channel length (L)

- larger channel width (Z)

- thinner oxide layer (C<sub>i</sub>)

- lower threshold voltage (V<sub>T</sub>) ,and...

- higher surface e mobility ( $\mu_n$ )

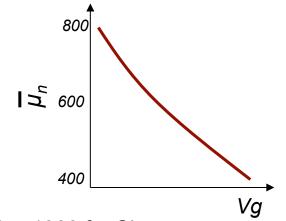

$\mu_n$  is ~1300 for Si... and  $\overline{\mu}_n$  lower due to rough

and  $\overline{\mu}_n$  lower due to roughness and fixed charge at oxide/Si interface... but why decrease with increasing Vg?

18 Drain Current

School of Electronics & Computing Systems

► It can be shown (6.5.1) that NMOS drain current for <u>all</u> V<sub>D</sub> values including pinch-off (saturation) is given by:

$$I_{d} = k_{N} \left\{ \left( V_{G} - V_{FB} - 2\phi_{F} - \frac{1}{2}V_{D} \right) V_{D} - \frac{2}{3} \frac{\sqrt{2\varepsilon_{s}qN_{a}}}{C_{i}} \left[ \left( V_{D} + 2\phi_{F} \right)^{\frac{3}{2}} - \left( 2\phi_{F} \right)^{\frac{3}{2}} \right] \right\}$$

$$k_{n} = \frac{\overline{\mu}_{n}ZC_{i}}{L} \quad \text{(transconductance parameter)}$$

$$V_{G} \geq V_{T} \quad V_{D} = V_{G} - V_{T} \quad V_{D} + \int_{D} \int_$$

SECS 2077 – Semiconductor Devices ©

Instructor – Prof. Jason Heikenfeld

UNIVERSITY OF

Cincinnati

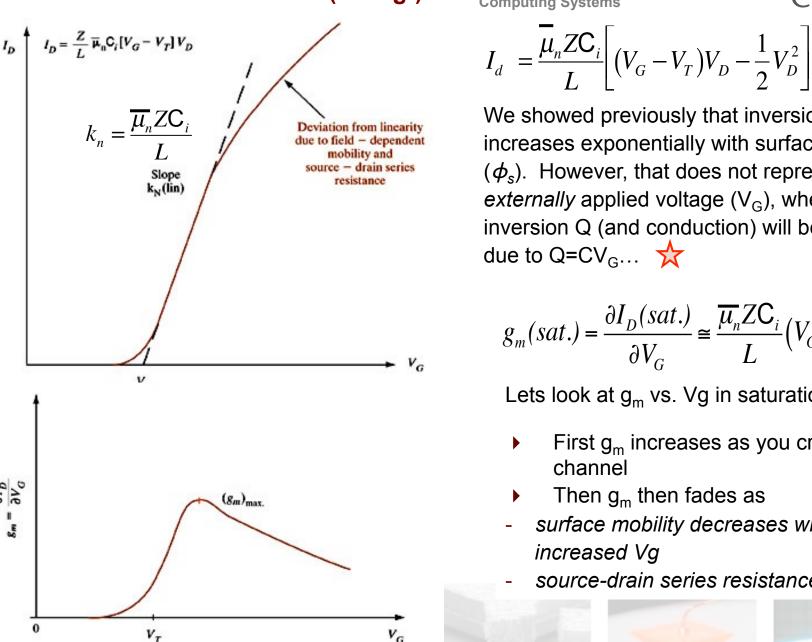

#### 19 Transconductance

▶ For NMOS in linear region where  $V_D << (V_G - V_T)$

$$I_d = \frac{\overline{\mu}_n Z \mathbf{C}_i}{L} \left[ (V_G - V_T) V_D - \frac{1}{2} V_D^2 \right]$$

► At saturation, no point in having effect of  $V_D$  in equation, so new term  $V_{D,Sat.} \approx (V_G - V_T)$

$$I_d$$

(sat.)  $\approx \frac{1}{2} \frac{\overline{\mu}_n Z C_i}{L} V_{D,Sat}^2$

► What is g<sub>m</sub> for the curves above?

$$g_m = (4-2 mA)/(2-1)V$$

$g_m = 2x10^{-3} mhos$

► An important parameter for MOSFETs is their transconductance: g<sub>m</sub>(sat.)

$$g_m(sat.) = \frac{\partial I_D(sat.)}{\partial V_G}$$

$$g_m(sat.) \approx \frac{\overline{\mu}_n Z \mathbf{C}_i}{L} (V_G - V_T)$$

SECS 2077 – Semiconductor Devices ©

20 Transfer Characteristics (vs. Vg!)

School of Electronics & **Computing Systems**

UNIVERSITY OF

SECS 2077 – Semiconductor Devices ©

We showed previously that inversion Q increases exponentially with surface potential  $(\phi_s)$ . However, that does not represent *externally* applied voltage ( $V_G$ ), where inversion Q (and conduction) will be linear due to  $Q=CV_G...$

$$g_m(sat.) = \frac{\partial I_D(sat.)}{\partial V_G} \cong \frac{\overline{\mu_n} Z \mathbf{C}_i}{L} (V_G - V_T)$$

Lets look at g<sub>m</sub> vs. Vg in saturation...

- First g<sub>m</sub> increases as you create the channel

- Then  $g_m$  then fades as

- surface mobility decreases with increased Vg

- source-drain series resistance kicks in...

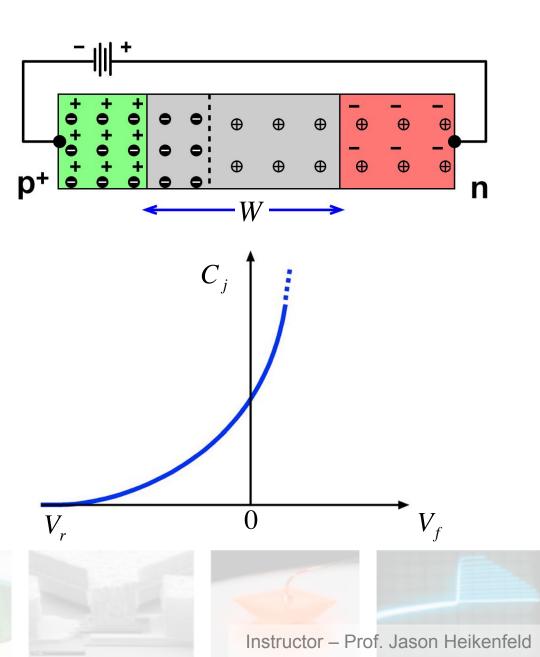

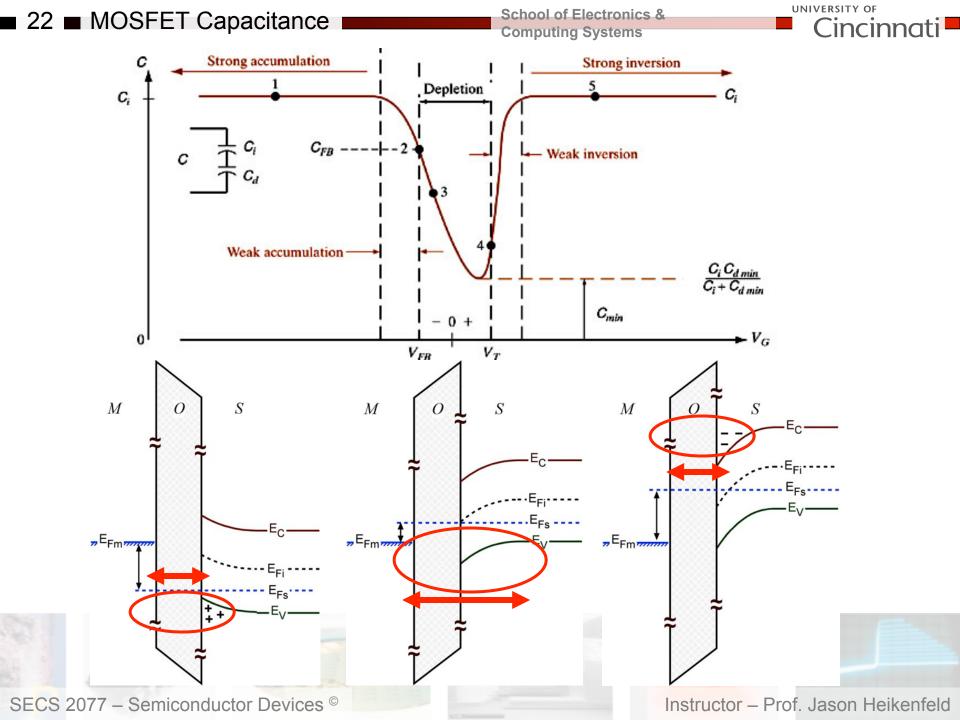

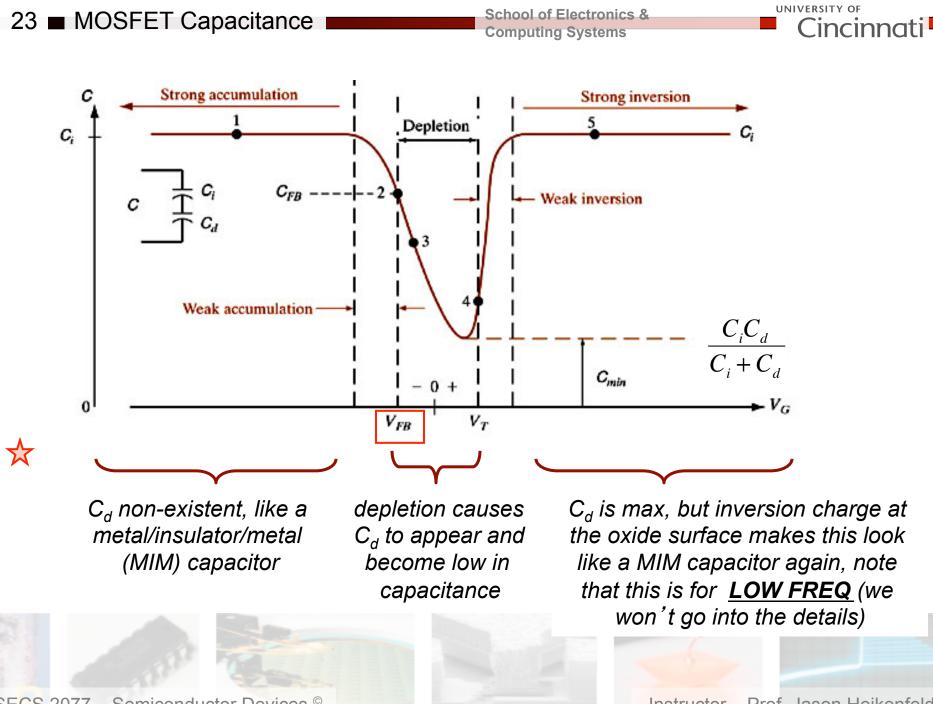

### ■ 21 ■ MOSFET Capacitance

School of Electronics & Computing Systems

Cincinnati

► Lets look at MOSFET Capacitance... (last topic)

▶ Recall that for a PN junction capacitance decreases with reverse bias voltage... (why?).

$$C_{j} = \frac{\varepsilon A}{W} = \frac{\varepsilon_{0}\varepsilon_{Si}A}{W}$$

• We should then expect a similar effect for the MOS capacitor, however... we also have to deal with accumulation and inversion!

SECS 2077 – Semiconductor Devices ©

SECS 2077 – Semiconductor Devices ©

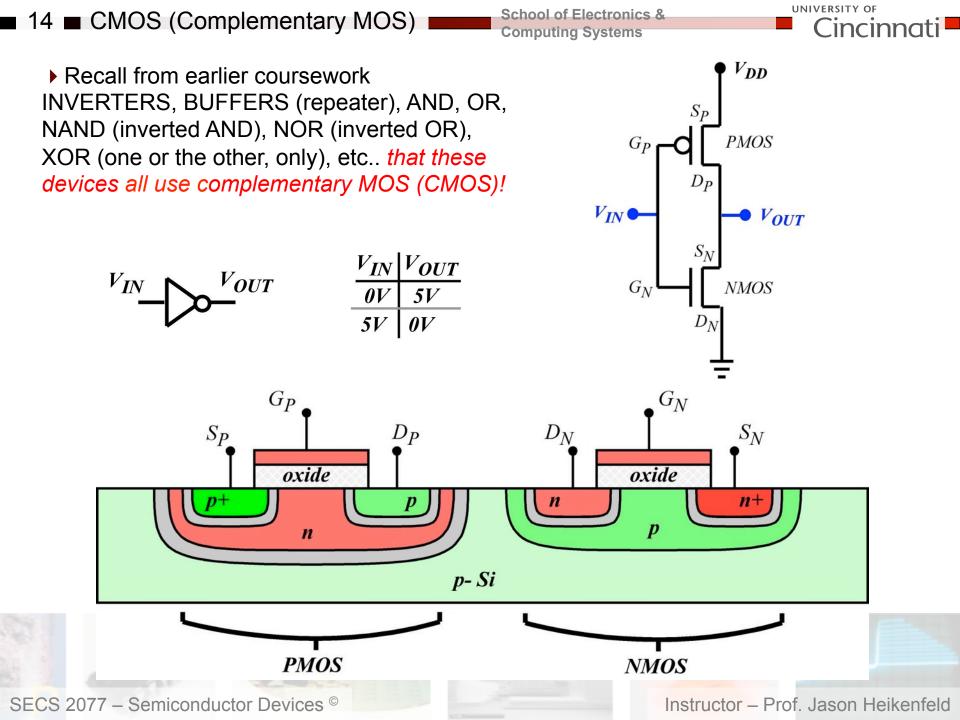

■ 24 ■ Review!

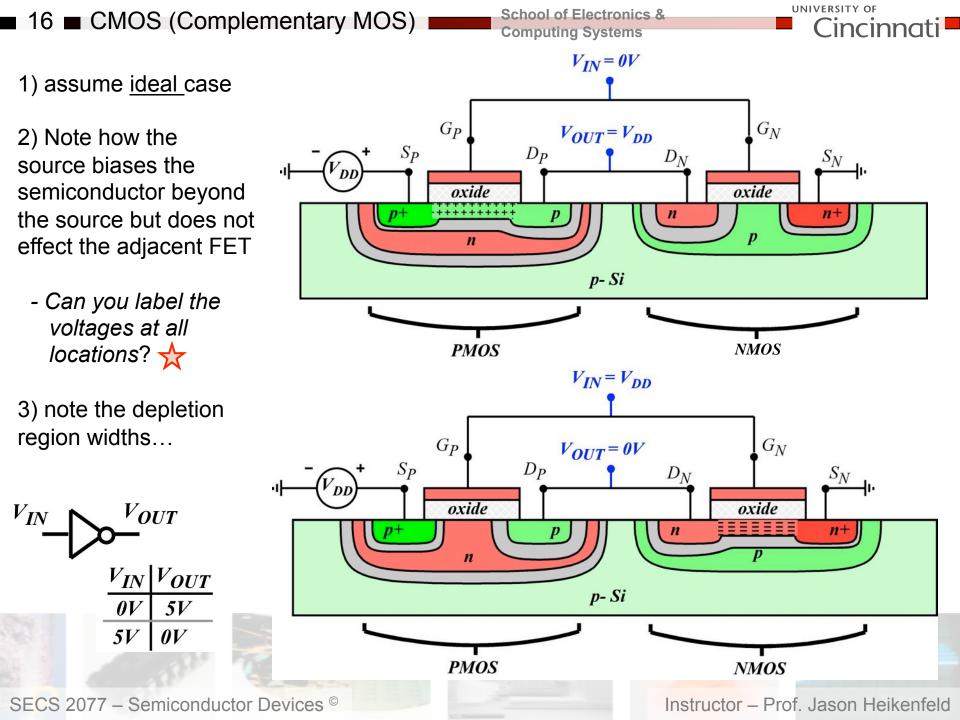

What terms for V<sub>T</sub> invert in sign for PMOS? (devices at right are NMOS)

What terms for V<sub>T</sub> shift for PMOS?

Roughly, what is the voltage in the p Si substrate for the device with voltage sources on it?

► How will the MOSFET capacitance change with V<sub>G</sub>? *There are three factors/regions of capacitance...*

► Is drain current vs. gate voltage (called transfer characteristic) linear or exponential, and what fundamental 3-variable equation determines why?

SECS 2077 – Semiconductor Devices ©

$$V_T = \phi_{ms} - \frac{Q_i}{C_i} - \frac{Q_{d,max}}{C_i} + 2\phi_f$$

$$g_m(sat.) = \frac{\partial I_D(sat.)}{\partial V_G}$$

■ 25 ■ For next time...

School of Electronics & Computing Systems

Cincinnati

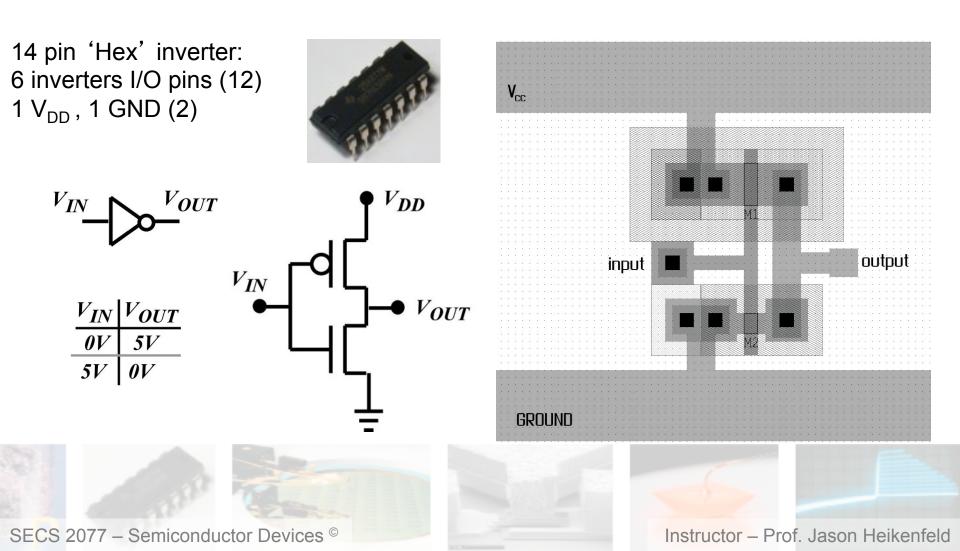

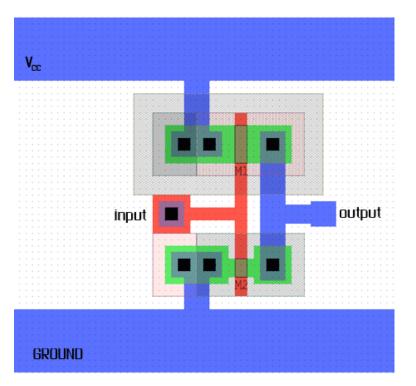

> This is an inverter.... will tell you next time what the layers are : )

SECS 2077 – Semiconductor Devices ©

www.sccs.swarthmore.edu/users/06/adem/engin/e77vlsi/lab3/

Funny, I randomly picked my colors for materials when starting this course and they seem to match up!